ご覧いただきありがとうございます。I2C通信を行うための回路をICやFPGA内部に作るための考え方について、ざっくりとまとめてみました。VerilogなどのHDL言語で設計されることが一般的かと思います。このような標準的なインタフェース回路は既に用意されているライブラリを使うことが多いのですが、動作の仕様を理解して、HDL言語で自作してみるのも面白いのではないかと思います。この記事では、I2C通信の仕様ではなく、I2C通信を行うための回路をICやFPGA内部に作りこむときの考え方についてまとめています。

I2C通信とは

I2C(Inter-Integrated Circuit)とは、フィリップス社(現在のNXP社)が提唱した、ICなどの部品間の通信インタフェースです。センサやEEPROMなど、比較的低速なインタフェースで使われることが多いです。通信の仕様自体は広く一般的に公開されています。例えばこちらのような記事がわかりやすいです。Rohm I2C|マイコンとは?

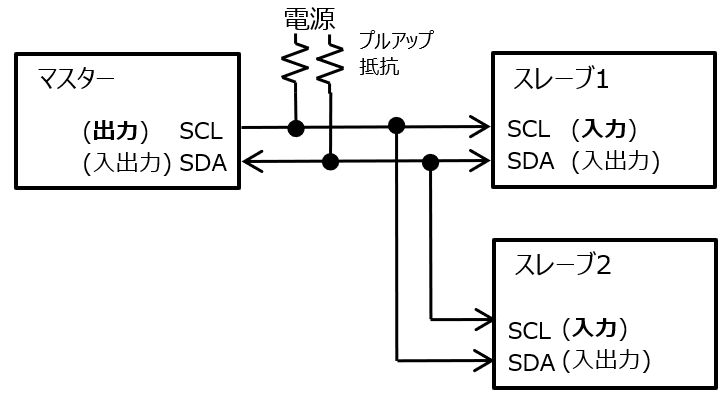

I2C通信の構成例はこのようなものです。SCL(クロック)とSDA(データ)の2本の線を接続して通信します。マスターになる部品が1つ、スレーブになる部品が複数で構成されます。

マスター:

マイコンやFPGAなど、通信を制御する部品。SCLを出力する。SDAは双方向でスレーブへ情報を送る際は出力、スレーブから情報を受け取る際は入力になる。

スレーブ:

センサICやEEPROMなど。通信を制御される側の部品。SCLは入力、SDAは双方向。他のスレーブとは異なるスレーブアドレスが割り振られており、マスターから指定されたアドレスが自身のアドレスと一致すれば自身が選択されたと認識できる。

SCLやSDAは、オープンドレイン出力で構成されています。以前の記事 便利な出力回路 オープンドレイン で構造をご紹介しておりますので、よろしければご参照ください。SCLは片方向なのでオープンドレインでなくてもいいように思われますが、SDAとの同期が必要ということもあるので、信号遅延をSDAと同じにするよう、SCLもオープンドレインで構成されることが多いようです。I2C通信は低速な通信ではありますが、一般に複数線で通信インタフェースを構成する場合は各線をできるだけ等長で遅延差がないように設計するのがよいと思います。

最近は設計現場であまり見られなくなった気がするI2C通信ですが、先日電子工作してみた ミニ・グランドピアノ でも使われていたので、一般的によく使われている通信方法なのだと思います。

IC内部の回路を考えてみる

IC内部の回路構成は、ざっくりとこんな感じかと思います。I/O部分はオープンドレインになっていて、内部回路からの出力はNチャネルMOSFETのゲートに入力されるイメージです。内部回路からの出力とICからの出力はMOSFETを経由することで反転の関係になります。一方、入力の方はドレインの状態をそのまま受ける形になります。この内部回路の部分を、VerilogなどのHDL言語で設計するのが一般的かと思います。

IC内部回路の動作

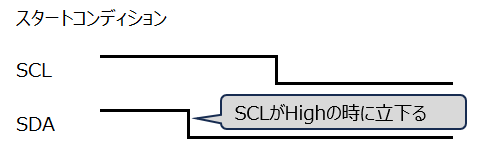

IC内部の動きを考えていきます。初期状態としてはSCLもSDAも出力しない(=オープン)の状態なので、外付けのプルアップ抵抗によって状態としてはHighになります。通信を始めるときは、マスター側によってスタートコンディションが作られます。

このように、SCLがHighの状態のとき、SDAをHigh→Lowに変化させることで、今からI2C通信を始めますよ、という合図になります。スレーブ側はこの状態を検知することで通信が始まることがわかります。この後、マスターからスレーブアドレスが送信され、該当するスレーブがACKを返す、・・・という感じで通信が進んでいきます。

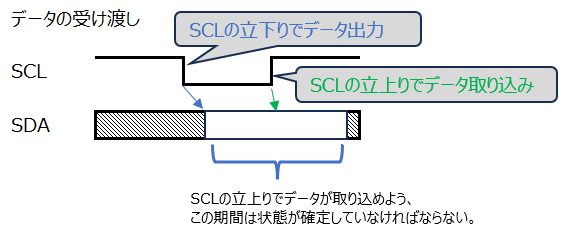

データの受け渡しはこんな感じ。SCLの立下りでデータを出力するICはSDAをオープン(=Highになる)かLowを出力します。データを出力しないICはSDAをオープンのままにしておきます。SCLの立上りでSDAの状態を受け取ります。

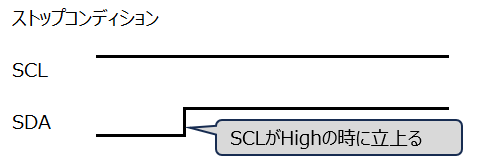

規定の通信が終わったら、マスターによってストップコンディションが発行されて通信終了となります。ストップコンディションは、SCLがHighの時にSDAをLow→Highに変化させることで発行できます。以上のような動作イメージで、マスター、スレーブとも状態遷移を作って回路設計していくことができます。外部からのクロックを使うことなくSCLとSDAだけで設計できるとは思いますが、I2C以外の回路に対して非同期で動作することになるので、他の回路へのデータ受け渡し部分は慎重に設計することが必要となるでしょう。

まとめ

ICやFPGAの内部で、I2C通信を行うための回路はどのようになるか、ざっくりとしたイメージをご説明いたしました。オープンドレイン出力の特徴を意識して、SCLとSDAの変化で状態遷移を設計することで回路設計ができそうです。私もかなり昔にこの回路をVerilogで設計したことがあります。非同期設計になるので、他の回路とのデータ受け渡しや、意図しない状態遷移を作らないようにするなど、実際やってみると結構難しかったように思います。最近はこういう標準的な機能は、あらかじめ用意されているライブラリを使用するのが一般的かと思いますが、動作仕様を理解してあえて手作りで設計してみるのも面白いのではないでしょうか。